## UNIVERSITY OF SWAZILAND MAIN EXAMINATION, MAY 2007

## **FACULTY OF SCIENCE**

## DEPARTMENT OF ELECTRONIC ENGINEERING

TITLE OF PAPER: DIGITAL ELECTRONICS I

COURSE CODE: E362

TIME ALLOWED: THREE HOURS

## **INSTRUCTIONS:**

- 1. There are seven questions in this paper. Answer any FIVE questions.

- 2. Each question carries a total of 20 points as indicated.

THIS PAPER SHOULD NOT BE OPENED UNTIL PERMISSION HAS BEEN GIVEN BY THE INVIGILATOR

THIS PAPER CONTAINS EIGHT (8) PAGES INCLUDING THIS PAGE

**Boolean Function Fundamentals:**

Q1a 10pts: Transform the Boolean function below,

A: MSB , D: LSB

$F(A,B,C,D,E) = (B + \overline{AD + C})(A\overline{B} + \overline{D}),$ into:

- (i). K-Map,

- (ii). Equation in SOP form,  $F_s = \Sigma(---)_{hex}$  (iii). Equation in POS form,  $F_p = \prod (---)_{hex}$

**Q1b 10pts:** prove  $F_p = F_s$

Q2a 10pts: Create a 4-bit reflected (Gray) code from the start byte, 1101.

Simplification:

**Q2b 10pts:** With the help of a K-map, obtain the simplified expressions in (1) SOP,  $F_s$  and (2) POS,  $F_p$  of the following Boolean Function, where d is the don't care case. Can you claim  $F_s$ = $F_p$  and explain why?

$$F(A,B,C,D) = \overline{A}(B\overline{C} + CD) + A\overline{B}C\overline{D}$$

$$d(A,B,C,D) = A(BC + \overline{B}D) + \overline{AB}(\overline{C} + \overline{D})$$

Q3 20pts: Using the tabulation method, simplify the following Boolean function F,

F(w, x, y, z)= $\Pi(0, 2, 4, 5, 6, 7, D, F)_{hex}$ (hex number in the brackets of the above function),

- (a) a product of sums; do directly under the process of the POS system;

- (b) a sum of products; transform F into  $F=\Sigma(...)$  and then do directly under the process of the SOP system.

Compare the two results if they are equal.

Combinational Logic Circuit:

Q4a 10pts: Implement the Boolean function below with only NAND gates and nothing but NAND gates, yet complement inputs are available only at input terminals, nowhere else. The implementation must have its function support.

$$F(A,B,C,D,E) = (A + \overline{B}D) + (\overline{A} + C)\overline{AB}C$$

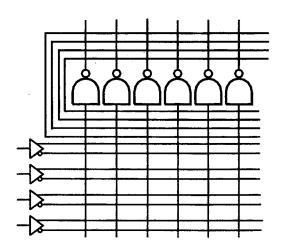

**Q4b 10pts:** Implement the function given below with a PAL structure. Simplification is required.

$$G(A,B,C,D) = (B + \overline{AD+C})(A\overline{B} + \overline{D}),$$

- Q5a 10pts: Using, as elementary components, basic gates and 4-bit full binary adders (which has of course a carry-in and a carry-out), design a one digit BCD Full-Adder including a carry-in and a carry-out, Find the adder circuit. (hint: it is simply a code converter.)

- Q5b 10pts: Use ROM to implement a binary multiplier that multiplies a 3-bit number A by another number B to form a product C of 6-bit. Be aware that the ROM address and the data are both always in Hex number and that the addresses are always continuously numbered. Find the specifications of the ROM (ie, the size of the address byte and the data byte) and the ROM content. How the address and the data are related to A, B, and Product? Vacant memories can be abbreviated by "...".

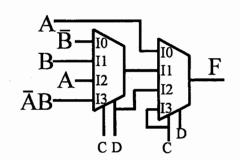

Q6a 10pts: Complete the 4-input K-map for the following Mux circuit.

| $\mathbf{C}$ | D  |    |    |    |

|--------------|----|----|----|----|

| AB           | 00 | 01 | 11 | 10 |

| 00           |    |    |    |    |

| 01           |    |    |    |    |

| 11           |    |    |    |    |

| 10           |    |    |    |    |

Q6b 10pts: You have two Quad 2-1 Muxs and one 8-1 Mux. Make use of these components to implement a larger Mux. The larger, the better it is. Give the circuit and the address arrangement.

- Q7a 16pts: 74LS85 is a 4-bit comparator. It has two sets of data inputs (A and B), input (A<B, A=B, A>B), and output (A<B, A=B, A>B). Use this IC to expand to an 8-bit magnitude comparator. Both circuit and support equations are required.

- Q7b 4pts: Modify 74LS85 to check if the two input data, A and B, are equal or not. Then, the circuit has only one output x, so that x=1 if A=B, and x=0 if  $A\neq B$