# University Of Eswatini Faculty of Science and Engineering Department of Electrical and Electronic Engineering

## Main Examination, December 2018

| TITLE of Paper:<br>Course Number: | Analogue Electronics I / Analogue Design I EEE321 / EE321                 |

|-----------------------------------|---------------------------------------------------------------------------|

| Time allowed 3 ho                 | urs                                                                       |

| Instructions:                     |                                                                           |

| 1. EE321 Stude                    | ents answer any Four (4) questions in Section A                           |

| 2. EEE321 stud                    | dents answer any Three (3) questions in Section A and One (1) question in |

| Section B.                        |                                                                           |

| 3. Each questi                    | on carries 25 marks.                                                      |

| 4. Marks for e                    | ach question are shown at the right hand margin.                          |

|                                   |                                                                           |

| This paper contain                | s 7 pages including this one.                                             |

#### Section A

#### Question 1

- a) State the three modes of operation of an NPN transistor and tabulate the bias conditions of the junctions.

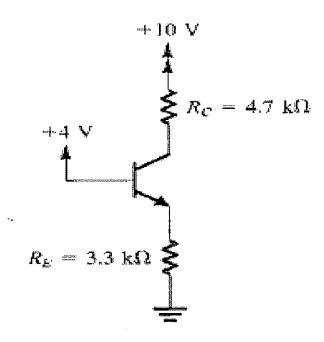

- b) For the circuit **Figure 1** below determine the node currents  $I_C$ ,  $I_B$  and  $I_E$  and determine the mode of operation of the transistor for  $\beta = 100$ .

- c) Draw the voltage transfer characteristics (VTC) of a MOSFET transistor and explain how the value of  $v_{GS}$  in relation to  $V_t$  affects the changes in the modes of operation of the transistor. Write the values of  $V_{DS}$  and  $i_D$  in the saturation region. [5]

- d) Describe how to find the current  $i_D$  of a MOSFET in terms of the charge Q per unit length and the electron drift velocity. Assume a small  $v_{DS}$  is applied to the transistor. [6]

Figure 1

### Question 2

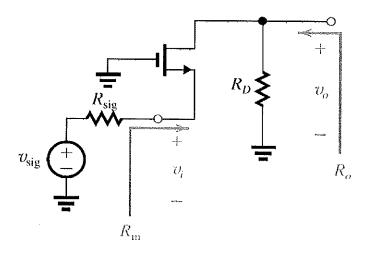

a) The circuit Figure 2(a) is the Common Gate amplifier

Figure 2 (a)

Find:

- i) Input resistance,  $R_{in}$ , the output resistance,  $R_o$ , and the open circuit gain  $A_{vo}$  [6]

- ii)  $G_V = \frac{v_0}{v_{sig}}$ , assuming  $R_L$  is connected at the output. [6]

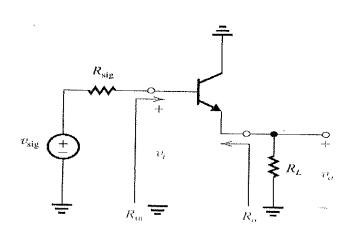

- b) Given the circuit shown in Figure 2(b) below,

- a. Draw the small signal equivalent circuit [3]

- b. Find  $R_{in}$  [6]

- c. Show that it has a gain of unity hence the name "Emitter follower" [4]

Figure 2 (b)

#### Question 3

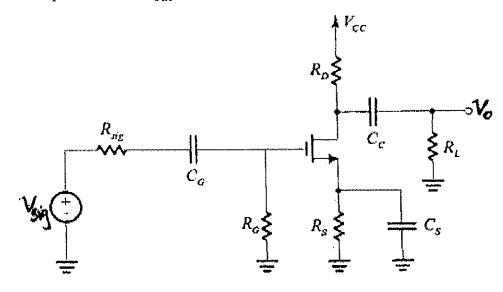

Consider the Common-Source amplifier circuit, Figure 3 below.

- a) Draw the small signal equivalent circuit. [3]

- b) Find

- i) The input resistance  $R_{in}$  [1]

- ii) The voltage gain  $G_V$  [4]

- iii) The output resistance  $R_{out}$  [2]

Figure 3

- c) For a Common-Emitter amplifier with Emitter resistance,  $R_e$

- a. Draw the circuit diagram and its equivalent circuit after using the *T-model* to replace the transistor.

- b. Find the following

- i. The input resistance  $R_{in}$ , [4]

- ii. The output resistance  $R_{out}$  and [2]

- iii. The overall gain  $G_{\nu}$  given that a load resistance  $R_L$  is connected at the output. [6]

#### Question 4

- a) A BJT operating at  $I_C=2mA$  has  $C_\mu=1pF$   $C_\pi=10pF$  and  $\beta=150$ . Calculate:

- i)  $f_T$  [4]

- ii)  $f_{\beta}$  [4]

- b) For the op-amp inverting integrator circuit,

- i) Draw and label the circuit diagram. [3]

- ii) Determine the voltage across the capacitor. [4]

- iii) Determine output voltage. [2]

- c) For a 0.08  $\mu m$  process technology for which  $t_{ox}=15nm$  and  $\mu_n=550cm^2/V$ . s. Given that the transistor is operating in saturation with  $I_D=0.2mA$  with  $\frac{W}{L}=20$ , Find

- i)  $C_{ox}$  [2]

- ii)  $k'_n$  [2]

- iii)  $V_{ov}$  [4]

#### Question 5

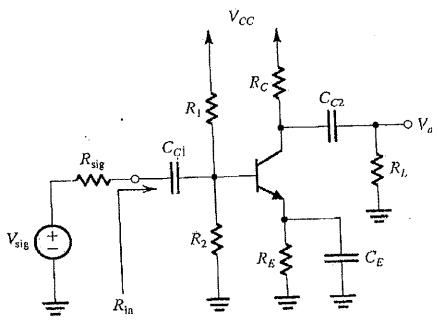

Consider the common-emitter amplifier shown in **Figure 5** under the following conditions:  $R_{sig} = 5k\Omega$ ,  $R_1 = 33k\Omega$ ,  $R_2 = 22k\Omega$ ,  $R_E = 3.9k\Omega$ ,  $R_C = 4.7k\Omega$ ,  $R_L = 5.6k\Omega$ ,  $V_{CC} = 5V$ ,  $r_0 = 300k\Omega$ ,  $\beta = 120$ , dc collector current,  $I_C = 0.3mA$ ,  $V_T = 25mV$ ,  $C_\mu = 1$  pF,  $f_T = 700MHz$ ,  $r_x = 50\Omega$ , Find

- a)  $C_{\pi}$  [5]

- b) The mid-band voltage gain  $A_M$  [8]

- c) The input capacitance  $C_{in}$  [4]

- d) The effective source resistance  $R'_{sig}$  [4]

- e) The upper-3dB frequency  $f_H$  [4]

Figure 5

#### Section B

#### Question 6

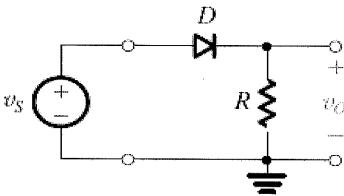

a) Given the half wave rectifier, Figure 6, below

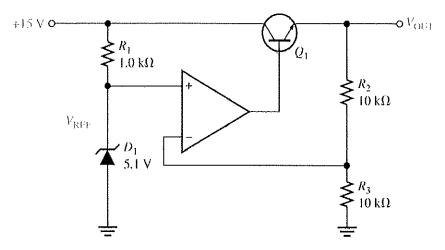

Figure 6 i) Find the RMS value of the load voltage [4] ii) Find the RMS value of the load current [4] iii) Given that the current  $i(t) = 5\sin(2\pi 100t)$  and the voltage is  $v_0 = 10 \sin(2\pi 300t)$  find the values of the RMS voltage and RMS current above. [4] iv) Show that the efficiency of the rectifier above  $\eta = 0.405$ [4] b) State three types of regulators [3] c) List and describe three elements of a regulator [6] Question 7 a) In the circuit Figure 7 below i) Identify the type of regulator. [2] ii) Identify the four elements that make up a regulator. [4] iii) Find the output voltage.

[3]

Figure 7

b) For a full wave rectifier

i) Find the mean value of the load current and the load voltage

ii) Show that its efficiency is 0.81

c) Describe the operation of a shunt regulator

[6]